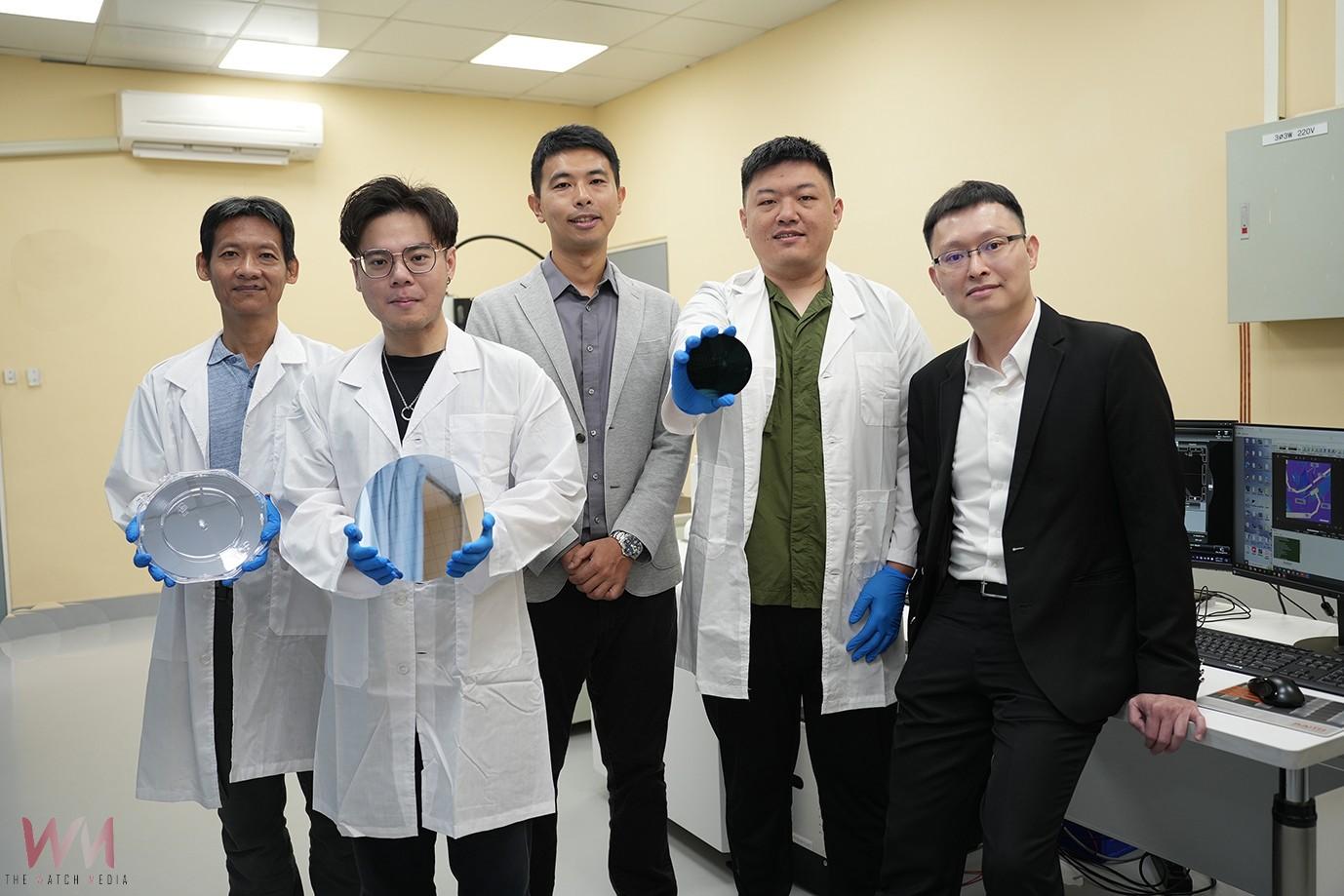

(觀傳媒中彰投新聞)【記者廖妙茜/台中報導】在國科會自然司、「尖端晶體材料開發及製作計畫」與「A世代前瞻半導體專案計畫」,以及教育部特色領域研究中心計劃的大力支持下,由中興大學與成功大學共組的研究團隊,成功研發出全球首見的「懸浮式鐵電膜整合二維電晶體」技術,為AI晶片、記憶體整合與3D封裝設計開啟全新想像。這項研究成果今年6月底正式發表於國際權威期刊《Nature Electronics》,展現台灣在半導體關鍵材料與元件整合領域的世界級創新實力。

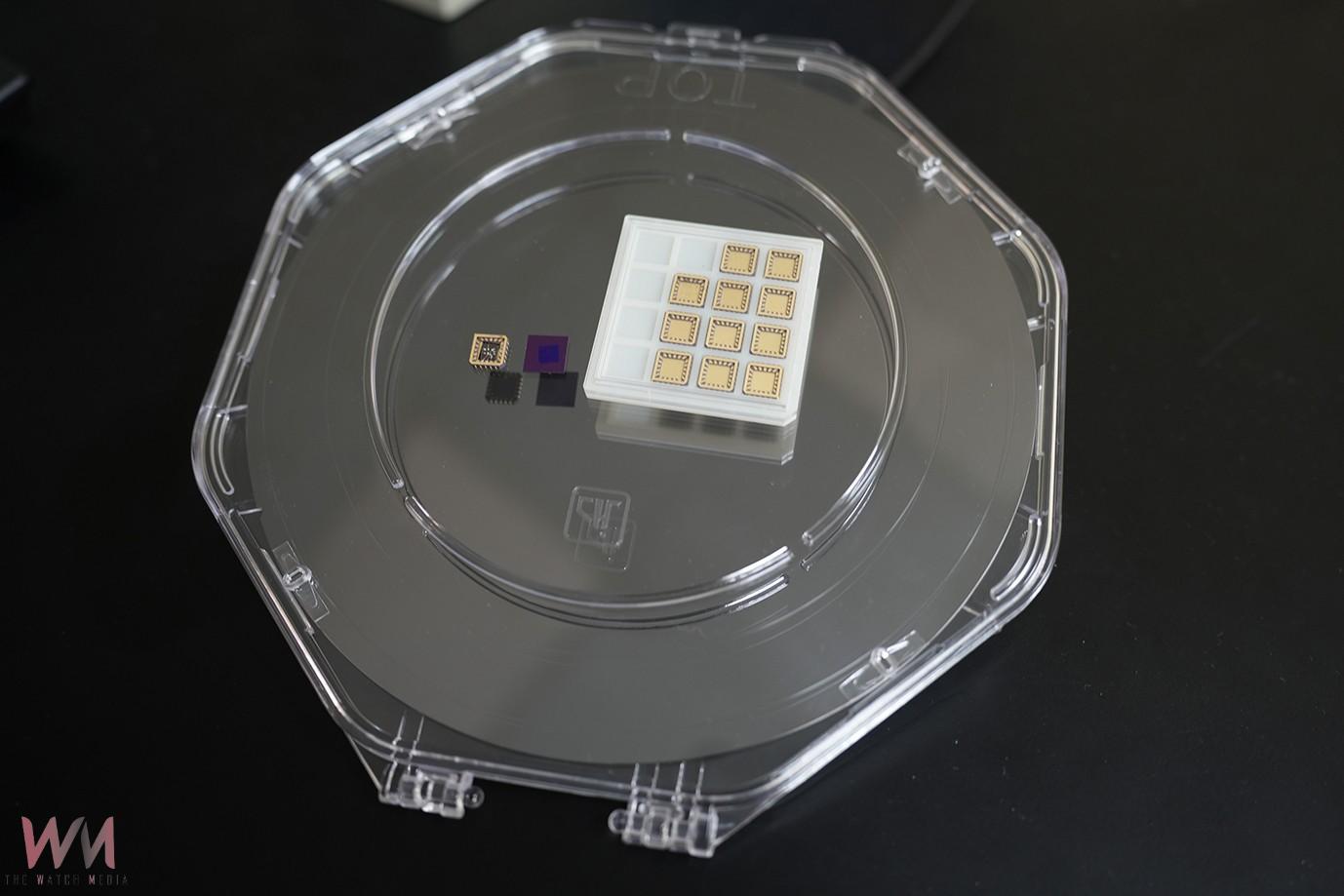

這項技術的最大突破,在於首度將鐵電材料 Hf0.5Zr0.5O2(簡稱 HZO)製成厚度低於 20 奈米、可自由轉印的懸浮式薄膜,並穩定且大面積地整合至二維半導體 MoS2 上,作為電晶體的高介電閘極絕緣層。這種新穎結構不僅克服傳統介電材料製程對 2D 材料造成損傷的問題,還展現出超過十億倍的開關比與僅53 mV/dec 的超低次臨界擺幅,在能效與效能表現上遠超現行主流技術。

傳統上,業界常依賴原子層沉積(ALD)或化學氣相沉積(CVD)技術製作介電層,但這些方法難以在不破壞二維材料的情況下實現高品質鐵電與高介電結構,且需額外繁複後處理,限制了元件在高效能與低功耗方面的發揮。相比之下,本研究所採用的懸浮式鐵電薄膜,具備高度轉印自由度與界面友善性,不僅讓製程更靈活,也為二維電子元件的未來應用打下嶄新基礎。

本研究通訊作者之一、中興大學林哲儀博士表示,「我們其實是把鐵電材料『解放』了,從過去只能固定在矽基板,變成像貼紙一樣可以自由貼合在任何想要的位置上」,他與碩士畢業生郭尚甫、蔡弦祺共同完成元件設計與驗證,他強調:「這不只是實驗室裡好量測的新材料,而是能真正跑、能運算、能做邏輯的實用技術,讓電晶體設計更靈活、功耗更低。」

在新穎材料開發端,成功大學楊展其教授團隊與兩位學生,劉祐承博士與陳柏材同學,掌握了懸浮式 HZO 薄膜的高品質製程與轉印關鍵能力,是技術成功整合的核心。楊展其教授表示:「我們讓鐵電材料從過去被動地附著在基板上,變成可以主動整合、自由配置的靈活介面。這種彈性,將在未來的記憶體、邏輯電路與 AI 晶片架構中扮演關鍵角色。」

中興大學林彥甫教授則帶領團隊從材料到元件完成一系列實作驗證,成功將該技術轉化為應用平台。「我們把這片懸浮膜變成一顆真正能工作的電晶體,甚至縮小到只有13 奈米的通道長度,仍能維持高效運作。」他指出,「從反相器、邏輯閘到 1-bit 加法器,我們一個個做出來,證明這不只是新材料,而是一套可模組化、可實用化的完整解決方案。」

隨著脈衝雷射沉積(PLD)設備的大尺寸擴展,這項懸浮式 HZO 膜技術未來有望導入8 吋乃至 12 吋晶圓製程,與現有半導體量產流程接軌,為台灣建立自主且前瞻的晶片製造技術樞紐。對一般民眾而言,這代表的將是更省電的 AI 手機、更耐用的穿戴裝置、更即時的智慧醫療設備,以及更節能的車用與感測晶片。當晶片變得更小、更聰明又更節能,我們的生活也將更智慧、更便利、更永續。